组合逻辑电路

电路在任一时刻的输出仅由该时刻的输入信号决定,而与该时刻以前的输入信号无关

组合电路通常由一些逻辑门构成,许多具有典型功能的组合电路已集成为商品电路(加法器,译码器)

竞争冒险

实际上,由于门电路延迟时间的关系,可能会使逻辑电路产生错误输出。通常把这种现象称为竞争冒险。

- 静态功能冒险

当有多个变量发生变化时,稳态输出不应该发生变化,但实际输出产生了毛刺

- 静态逻辑冒险

单个变量变化时,稳态输出不应该发生变化,但实际输出产生了毛刺

消除方法

- 修改逻辑设计

只适用于逻辑冒险

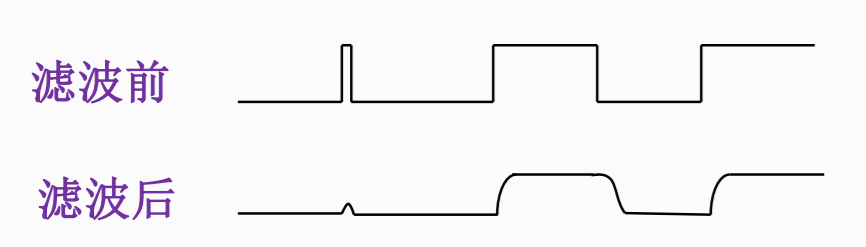

- 接入滤波电容

如果逻辑电路在较慢速度下工作,为了消去竞争冒险,可以在输出端并联一电容,其容量在几十~几百皮法之间,该电容和门的输出电阻构成RC低通网络,对窄脉冲起平滑作用

- 加选通脉冲

在包含时序电路的复杂数字系统中,可以用时钟信号的适当形式作为选通脉冲,消除数字系统中的竞争冒险

常用组合逻辑功能器件

编码器

将信息(如数和字符等)转换成符合一定规则的二进制代码

- 二进制编码器

- 输入互相排斥的编码器

- 优先编码器

- 对输入信号按轻重缓急排序, 当有多个信号同时输入时, 只对优先权高的一个信号进行编码

- 二-十进制编码器

- 输入: I0 ,I1,I2 ,…,I9, 表示10个要求编码的信号

- 输出: BCD码。

译码器

译码是编码的逆过程,将一组码转换为确定信息

- 二进制译码器

- 二-十进制译码器

数据分配器

数据分配是将一个数据源输入的数据根据需要送到不同的输出端上去,实现数据分配功能的逻辑电路称为数据分配器。分配器又叫多路复用器

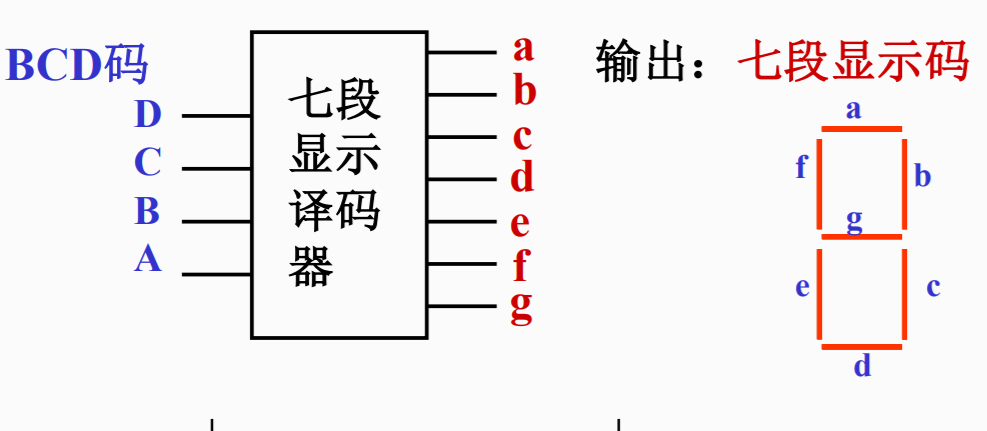

显示译码器

七段数码显示器

- 半导体数码管

- 液晶显示器

- 反射式液晶显示器:使用的可见光是环境光线

- 背光式液晶显示器:可见光由在显示器内特制的小光源提供

译码器应用

- 器实现组合逻辑函数

- 计算机输入/输出接口

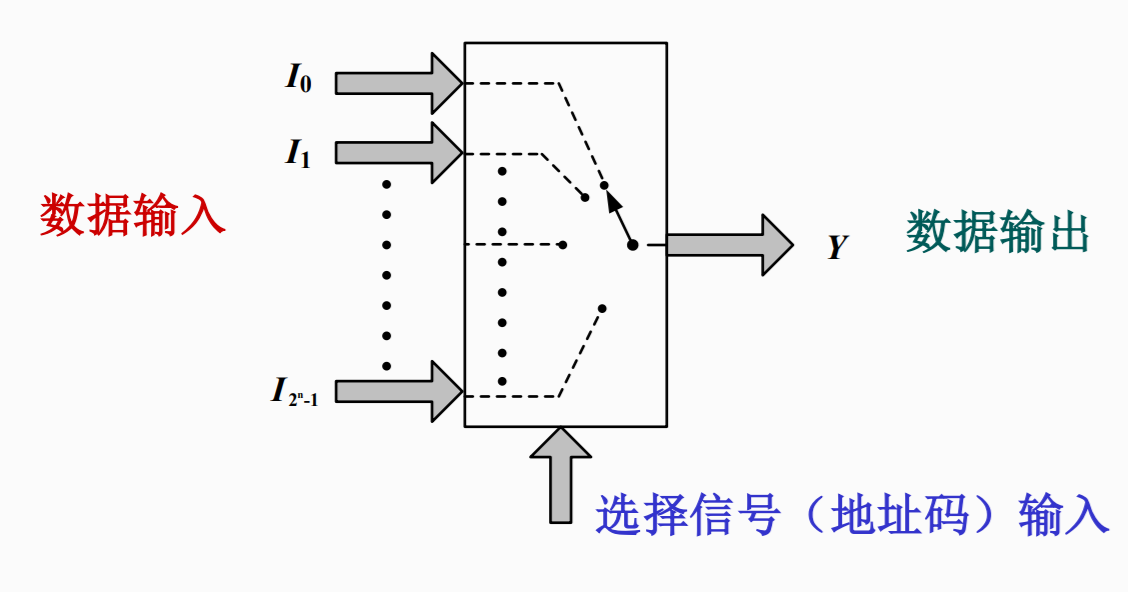

数据选择器

从多路输入数据中选择其中的一路送至输出端

动态显示电路

七段数码管驱动电路可分为两种,一种称为静态显示(每一个数码管由单独的七段显示译码器驱动),另一种称为动态显示(使用数据选择器的分时复用功能,将任意多个数码管的显示驱动,由一个七段显示译码器来完成)

加法器

算术运算电路的核心为加法器

- 半加器

仅考虑两个一位二进制数相加,而不考虑低位的进位,称为半加

- 全加器

在多位数相加时,除考虑本位的两个加数外,还须考虑低位向本位的进位

- 串行进位加法器

当有多位二进制数相加时,可模仿笔算,用全加器构成串行进位加法器,结构简单,运算速度慢

- 全并行加法器

速度最快,电路复杂

- 超前进位加法器

由两个加数,首先求得各位的进位,然后再经全加器算出结果

数值比较器

用来判断两个二进制数的大小或相等

比较两个多位数,应首先从高位开始,逐位比较